第3回FPGA エクストリーム・コンピューティング

第3回 FPGAエクストリーム・コンピューティングに参加して発表してきました。

すごく面白い会でした。

http://connpass.com/event/3118/

発表順が1番@ksksue 2番@kis 3番が自分だったので、二人が遅刻して自分がトップバッターになる覚悟をしていましたがw、無事@ksksueがギリギリ到着

1. FPGAのUIにAndroidを使う @ksksueさん

https://docs.google.com/presentation/d/1ATijR5A1NWiNFGJ-6__EO7Zn_bpiHxP6KFeQ20OMl3E/edit#slide=id.p

FPGAとAndriodを接続してAvalon bus上の一つのモジュールとしてAndroidが見えるようにしたお話。自分としてはおまけで話していたAndroidからFPGAをコンフィグする話の方が気になった。

2. mjpeg stream viewer on FPGA (自分)

OSC kansai@kyotoの資料におまけを追加して発表

最後のおまけで喋った渋滞の話は無理やり考えた妄想ですが、センサーネットワークのサーバーサイド realtime stream processingの所でFPGAがはまりそうという直感は本当。特に複雑系の社会全体のエネルギーを減らすようなアプリケーションにハマるんじゃないかと。

理由としては大量の入力に対して連携度を抜きだす部分でFPGAで高速化できそうという所と、多出力であっても演算は共有部分が多そうでハードによる高速化が効きそう。あとは、貯めていっているデータからの学習で演算を書き換えるのとかもFPGAにはまりそうかなと。

まだ、stream computing自体を良く分かってないので、明言はできないですが。。。

3. 高速シリアル通信を支える技術 @natsutanさん

@natsutanさんは、自分の中では "コアな技術者なのに対人スキルがすごい高い人"というイメージで、今回も発表の技術的な内容よりも発表の仕方の方に注目してしまいました。ここら辺を見習いたい。

4. 一般プログラマはどのようにFPGAを使うか @kisさん

最初に資料を前もっていっぱい作ってきたことに驚いたがw,これから日経ホニャララの記事になる内容だそう。

自分はGPGPUの利点欠点の所がめちゃ気になった。 software処理 vs FPGA vs ASICの利点欠点は常に言われているけど、最近はGPGPUも比較対象にあげられるようになっている。分かった部分と分からなかった部分があったので、福岡に帰ったら直接聞いてみる。

5. JavaRockでBlokusDuoプレーヤを作ってみる話 @miyoxさん

enchantMoon祭りと 日本のハードウェアと プロダクト+アクティビティ

enchantMoonが巷を騒がせてます。enchantMoonの喧騒は色々感じる物があって。

(それを書くと非難受けてしまうかもしれないけど。)

最初に以下のことは明示しときます。

・enchantMoonは、周りに持ってる人いないのでまだ触ってない

・LSIの量産はそれなりに知ってるけど、ガジェットの量産は素人

・ハードウェアとソフトウェアの開発者だけど、どちらかと言えばハード寄り。

触ってもないのに書くんじゃねえよって言われそうだけど、本当に言いたいことは一番最後の部分なんで。。。

enchantMoonはネットでハード屋さんから色々叩かれてるけど、コンセプトモデルとしてはこんなものなんじゃないかなと思う。普通はTS(テストサンプル),ES1(エンジニアリングサンプル), ES2,... とかハードウェアの修正を繰り返してから販売なんだろうけど、とりあえずTSとESの間で販売しちゃったぜみたいな印象。確かに、どこかのHPで見たフレキを直にはんだ付けってのはグッと来るけど(筐体に入れた時に応力かかって、常用使用で振動受け続けて大丈夫なのかな?)、大企業でもTSはこんなものなんじゃないかな?(大企業はTSを販売するなんてことは絶対しないけど。) あとはしばらく使用してボロボロと故障が出てきたらヤバイけど、なんとか一年ぐらい乗り切ればコンセプトモデルなんで使い続けるひとなんてホンの少し。TSからES1, ES1からES2, 試験-設計修正-製造-試験のループを1回廻すと物凄いお金がかかるので、そこら辺はギャンブルに出たって理解した。

ハードウェアってのは一箇所でもミスがあると全く動かなくなるので、とにかく一つもミスがないように物凄く気をつかって設計する。逆にソフトウェアは今までに無いものをcreationできるかが勝負なので少々のミスなんて気にしてたら面白い物はできない。日本のハードウェアは本当に信頼性が高くて世界的なブランドになっているので、TSレベルの物を製品のように言って売るのが受け入れられないハード屋さんがいるのも想像に難くない。

ネットの感想みてると、「使いものにならない」「面白い」「将来に期待」「ゴミ」..... 賛否両論で物議をかもしてるなぁという感じ。けど、物議を醸すというのはそれだけで物凄く価値があることなんだよね。社会に新しい価値を示しているからこそ評価が別れるわけで。

今のところ、現状は使えないって言ってる人の方が多いっぽいけど、本気の返品騒ぎは起きてない。つまりは使えないけど39,800円は払うって人が多い。それはつまり「製品+enchantMoonのアーリーアダプターになる行為」に39,800円払ったってことなんじゃないかと。これが大企業だったら袋叩きだったろうけど、UEIのチャレンジを応援することにお金払ってるんじゃないか。

元々Linuxから不完全なままリリースして、参加者を募るっていうバザール開発が始まってるけど、最近はgoogle glassとかでもハードウェア含めてその手法が適用され始めてる。さらにクラウドファンディングを通して、エンジニアでない人もお金で参加するということも始まってる。

昔は、専門知識を一杯持ってる人が尊敬されたし、最新の情報を持ってる人がカッコイイと言われたけど、今はググれば大抵の情報は手に入る。以下の記事(全面賛成する訳ではないけど。。。)でも、かっこ良く消費する時代から、かっこ良く生産する時代になったという部分は誰もが感じてるんじゃないか。

http://www.huffingtonpost.jp/rootport/post_5294_b_3668535.html

enchantMoon買った人は、日本から全く新しいタブレットを出すという、格好良い生産行為に参加する(パトロンになって応援する)アクティビティを購入したんじゃないかと感じる。もし、enchantMoonの完成度が完璧だったら、「面白いUIだけど、それだけだよね」ってなってたかもしれない。UIの革新性とかよりも、この手法の新しさの方がenchantMoon祭りの本質なんじゃないか。

あまりうまくまとまってないけど、完璧なハードウェアを販売するってのは当然メインストリームなんだろうけど、一部では完全ではないハードウェア+アクティビティを販売するというマーケットが育ち始めてるってのを感じたのが個人的なenchantMoon祭りの感想だった。

Yamaguchi Mini Maker Faire

Yamaguchi Mini Maker Faire に出展してきました!

今回は福岡勢が大勢参加。Maker Faire Tokyoとはまた違った楽しさのイベントになりました。想像してたよりも沢山人が来た。

前回のMaker Faire Tokyoで展示した見つめるぬいぐるみを再び展示してきました。Maker Faire Tokyoの時はADK2012を使ってたんだけど、今回3日前にショートさせて火花を散らせて壊してしまいました。急いでarduino-MEGA-ADKに変更。なんとか間に合ったけど、ちょっとバギーだったw

ぬいぐるみ 創り始める時に明確な意図を持っていて「見た人のエモーションを揺らす」ってのがテーマでした。

・ロボットは周りの人がそこに生き物がいるかのように感じることが最重要

・動きはどう頑張ってもロボットっぽさが消えないので、逆に外側がその動きが似合うようなデフォルメされた物の方が良い。

・顔認識がエモーション揺るがすのに物凄く有効

で、だいたい意図は成功したんだけど、今回のMakeで自分が思ってもみなかった発見があった。

ちょっとバギーなシステムだったので、時々グルンと一周したり、ガタガタ震えたりするんだけど、見てる人達はその時にめちゃくちゃ喜ぶ! 「二人画面に入ると、どっち見ていいか分からなくなって挙動不審になるんですよ〜」って説明してたんだけど、その不完全さがカワイイらしい。その瞬間目が輝いてテンションがあがってるのがはっきり分かる。

という訳で、エモーションを揺らすには、外側がデフォルメされた物が良いってのは正解だけど、モーションも不完全っぽい物の方が有効ってことを発見しました。特にバグ動作は意図して作ったものよりも有効みたい。

「不完全な部分に愛情を感じる」ってところが、哲学的だなぁなんて感じました。

オープンソースカンファレンス Kansai @Kyoto

ソフトウェア技術者のための電子回路 再学習: キルヒホッフの第二法則

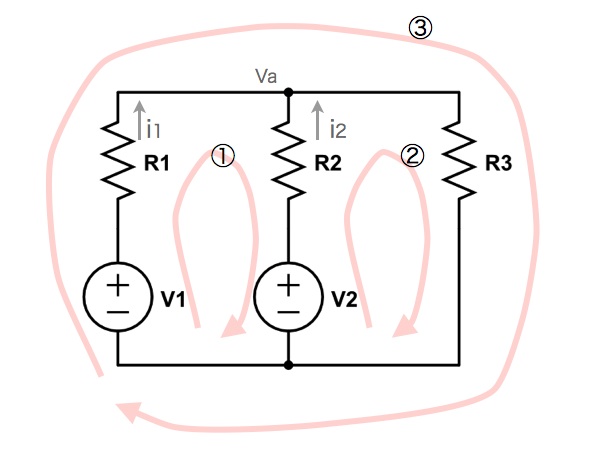

キルヒホッフの第二法則も直感で理解できます。

「電気回路網で"任意"の閉路を取り閉路に沿った各素子の

電圧Viの総和は0である」

要するに閉路をぐるっと回ってくると元の電圧に戻るよという意味です。

仮に今、上記のような電気回路網があって、"定常状態"の時、ループ①、ループ②、ループ③すべてにおいて、一周回って計算した時に電圧の総和が0になります。

(電圧の向きに注意)

ループ① V1 - R1 x i1 + R2 x i2 -V2 = 0

ループ② V2 - R2 x i2 - R3 x (i1 + i2) = 0 (キルヒホッフの第一法則よりR3の電流= i1+i2)

ループ③ V1 -R1 x i1 - R3 x (i1 + i2) = 0 (同上)

電池と抵抗でできた回路網の場合、キルヒホッフの第一法則と第二法則で"定常状態の"各点における電圧と電流を求めることができます。

電圧という言葉は、電流を流そうとする圧力のことで、本来ならば回路網の中のある2点を指定して"このポイントとこのポイントの電圧(=電位差)が**V"というのが正確な使い方です。

ただし、実際の電気回路にはグラウンドと呼ばれるポイントが少なくともひとつ以上あるのが普通で、そこを0Vとして、ある一つのポイントが**Vという言い方をすることもよくあります。

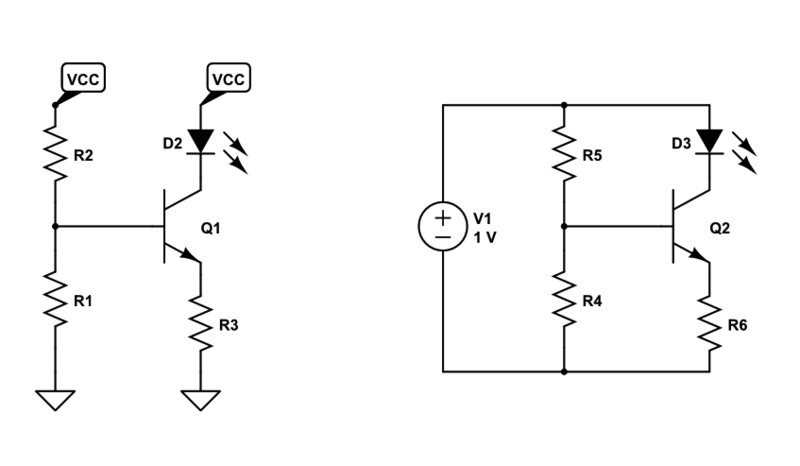

回路図をみると以下のような記号が一つ以上含まれているのが普通です。

(この二つの記号は同じ意味です)

ここを0Vと考えます。

複雑な回路図になるとグラウンド記号が沢山含まれているのが普通です。

その時、このグラウンド記号は全てつながっています。ですので、回路図をぱっと見た時につながっている部分以外に、くるっとつながっている”回路"が存在していることを頭の中で理解する必要があります。

左のような回路図は実際には右側のような回路網であり、この回路網の中で電流の変化や電圧の変化が起きて、何らかの回路の動作の意味をもっていることを理解する必要があります。

時間的な変化にも様々な種類があって、ある定常状態から別の定常状態に変化することに意味がある回路の場合は(例えばスイッチのON-OFFで状態を変える回路)、キルヒホッフの法則を二つの回路網(スイッチONの回路網とスイッチOFFの回路網)に適用して動作を理解します。

以前に説明したように、正弦波の変化に意味があるような回路の場合はキルヒホッフの法則で定常状態の各点の電流や電位を求めた上でどのような変化があるかを考えます。

BLOG 統合しました。

テクノロジー系のBLOGこっちに統合しました。

FPGAキットで始めるハード&ソフト丸ごと設計

CQ出版社からブログの内容に加筆して

「FPGAキットで始めるハード&ソフト丸ごと設計: CPUと周辺回路を作り込んでCプログラミング」

を出版しました。

<img src="http://blog-imgs-62.fc2.com/f/p/g/fpgadesign/cover.jpg" alt="cover.jpg" border="0" width="300" height="300" /></a>">

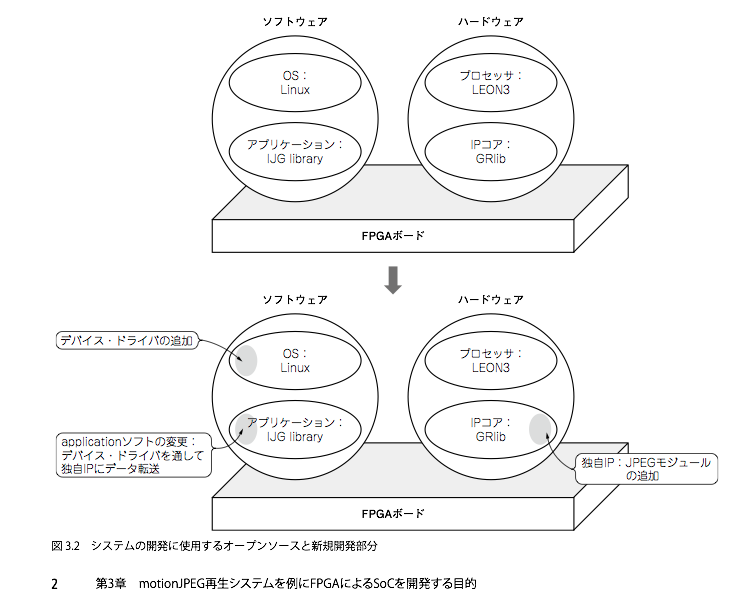

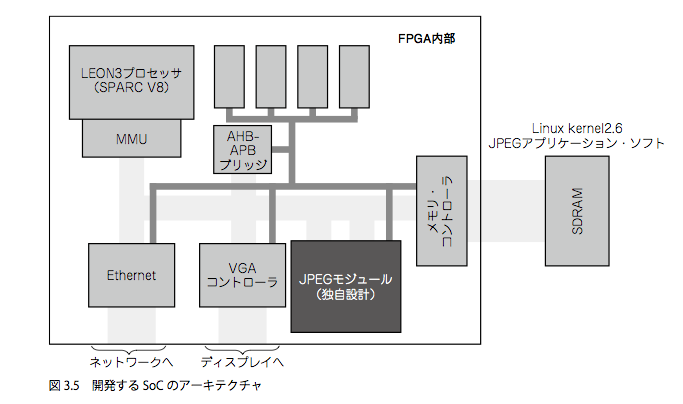

ブログの内容と同じく以下の様なシステムをFPGA上に開発します。

FPGAの中は以下の図のようなSoCでLinuxが動作しています。

すべてのソースコード( ハードウェア:VHDL, OS: Linux, アプリケーション&デバイスドライバ : C)はGPLライセンスでsourceforgeで公開しています。

最初にJPEGハードマクロが無い状態でストリーミング再生を行います。FPGAのCPU性能は低いため紙芝居のような再生となります。そのシステムでプロファイラを動作させて処理の重さを測定します。処理の重いJPEGデコードをハードウェアにオフロードすることにより高速化され紙芝居が通常の動画再生のレベルにまでなります。

ブログの内容に、ソフトウェア処理とハードウェア処理においてチップの中でどのようにデータ処理が行われているのかの解説を付け加えています。(1)単純な演算処理でのソフトウェア処理とハードウェア処理の違い(2)システムにおいてソフトウェア処理とハードウェア処理の違いを理解できるようにしました。ハードウェア処理はソフトウェア処理と異なり、並列動作が可能なこと、1クロック内であれば直列につないで処理できることを理解できるようにしたつもりです。

Appendix的にAMBAバスの説明を付けています。

対象読者は、FPGAの使いこなしは既に知っているが、小規模なロジックの実装しかしたことがなく大規模システムの開発がどのような物か知りたい人です。優秀な大学院生や企業の新入社員等をイメージしました。

実習書的な側面が大きく実際に動作させることによって理解できるようにイメージしています。

FPGA内部の設計データがハードなのかソフトなのかという話を出版社と色々しました。VHDLコードはそのままASIC化ができるハードウェアの設計データでもあり、FPGAにマッピングする限りはソフトウェア相当と見るべきという考え方もあります。ココらへんはオープンソースハードウェアのまた一つの別の流れだと私は思っていてオープンソースハードウェアというムーブメントを広めるという私の個人的な意思があります。その時のユーザーニーズとしては教育が一番分かりやすいのかな?という感覚があります。

すべてがGPLライセンスでgitで公開しているため、以下のような開発をgit上で開発していくイメージとなります。

既に大規模システム設計できるレベルのエンジニアの方にはこの事でハードウェアもオープンソース化やバザール開発への扉が開きつつあることを感じてもらえるのではないかという期待もちょっとあったりします。