LEONシステムのコンフィグレーション GR-XC3S-1500(Xilinx)編

必要なソフトウェアのインストールが終わったら、LEONシステムのコンフィグレーションを行います。

cd designs/leon3-gr-xc3s-1500

でボード用の開発ディレクトリに移動します。

このディレクトリには、Makefileが準備されていて、必要な作業はMakeコマンドで行えるようになっています

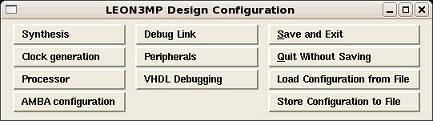

make xconfig

と打ち込むとGUIが立ち上がります。

基本的に、このボードに合わせたコンフィグレーションがすでに行われているので変更しなくても良いのですが、Synthesisから順に見ていきます。

Synthesisと書かれたボタンをクリックすると以下のようなGUIウィンドウが立ち上がります。

このディレクトリでGUIを立ち上げた時点で、GR-XC3S-1500に合わせた設定が行われています。

Target technologyには、Xilinx-spartan3が選択されています。

ここでは、何も変更する必要はありません。

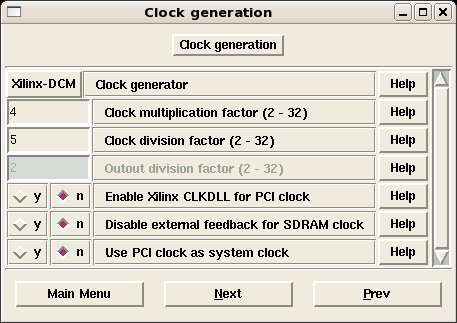

そこで Next のボタンをクリックすると、次の Clock generation に関する設定GUIウィンドウが立ち上がります。

クロック生成に関する設定項目が出てきますが、ここでも何もいじる必要はありません。

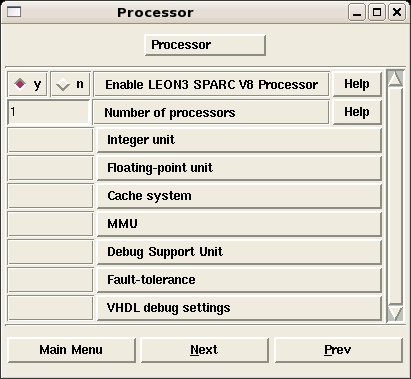

Next のボタンをクリックすると Processor のコンフィグレーションに関する設定GUIウィンドウが立ち上がります。

プロセッサに関してはコンフィグレーション可能項目が多数存在します。

まず、 Next のボタンをクリックすると、Integer unitのコンフィグレーションに関する設定GUIウィンドウが立ち上がります。

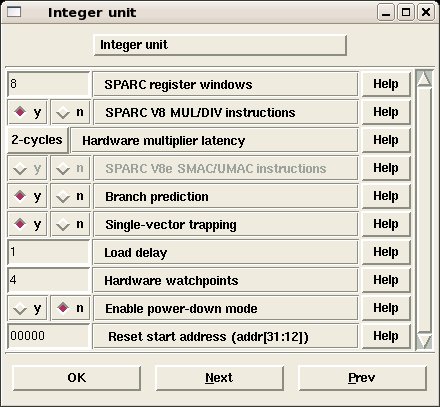

ここでも基本的にこのまま設定を変更しません。

最初の設定項目は、SPARCアーキテクチャ特有のregister windowの数です。

次は SPARC V8 MUL/DIV命令を実装するかどうかの選択です。実装しなかった場合乗算除算は別の小さな命令の集合でコンパイラが実現します。ここの設定によってコンパイラへ与えるオプションが変わります。

その他、分岐予測を行うかどうか等を設定できます。

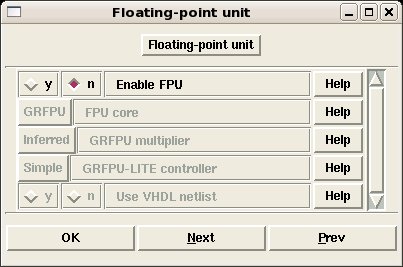

次に Next のボタンをクリックすると、FPU(Floating point unit)のコンフィグレーションに関する設定GUIウィンドウが立ち上がります。

FPUは、GPLライセンスでソースコード公開されておらず、コマーシャルライセンスが必要となります。ただし、Xilinx, Alteraで使用する際には、マッピングされたネットリストを評価ライセンスとして公開されています。これをダウンロードしてくれば、FPGAにマッピングして使用することは可能です。今回はFPUは使いません。

Nextボタンをクリックするとキャッシュのコンフィグレーションに関する設定GUIウィンドウが立ち上がります。

instruction cache, data cacheそれぞれに細かいコンフィグレーションが可能です。キャッシュ無しにすることもできます。キャッシュのサイズ、way数等を設定できます。

NextボタンをクリックするとMMUのコンフィグレーションに関する設定GUIウィンドウが立ち上がります。

長くなってきたので次のエントリへ続きます。