YCbCr-RGB変換モジュールRTL AMBA master(仮)

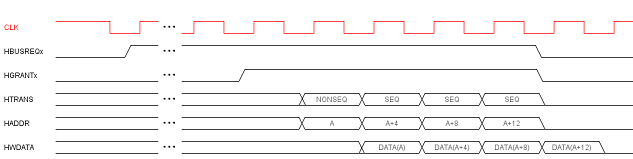

すでにスレーブの所で説明されていますが、この図には、マスターがバスの所有権を要求する所から示されています。また、バーストで複数データを送る際のHTRANS信号も示しています。

マスターは任意のタイミングでバスを要求することができますが、アービタからGRANT信号がアサートされるまでは、バスを使用することはできません。

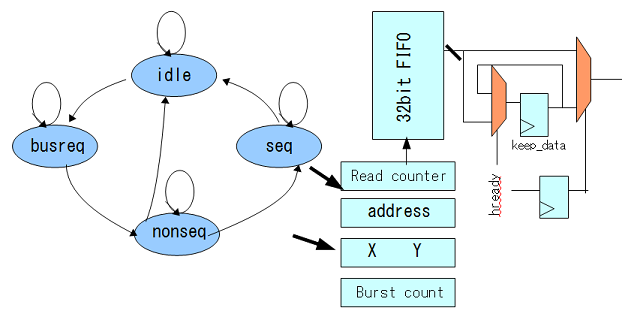

YCbCr-RGB変換モジュールでは、FIFOに蓄えられているデータの要素数(ライトカウンタとリードカウンタの差)が16以上になると、HBUSREQ信号をアサートします。

アービタからHGRANT信号がアサートされるまで要求し続けます。

所有権が認められたら、最初のアドレスを出力し、順次アドレスをインクリメントしていきます。その際、一つクロックがずれたところで対応するデータを出力します。またこれらの動作の際にHREADYがアサートされた時は現在出力している信号をそのまま出力し続けます。

基本的に16個のデータをバーストで出力したらバスを開放します。

画像はフレームバッファの左上に詰めて出力するようにしていますので、一行分のデータを出力したのち、出力先のアドレスが飛ぶことになります。この場合バースト動作ができませんので、そこでバースト終了してバスを開放します。

これらの動作をそのままFSMで設計しました。

FIFOに蓄積されている要素数(Write counter, Read counterの差)が16を超えたらBUSREQに移りHBUSREQをアサートします。

GRANTされるまでその状態を続けます。

GRANTされた後にHREADYが1であれば、最初のアドレスを出力します。

以後、バースト出力を続けます。

x,y座標や出力アドレス、FIFO read counter等のカウンターを動かします。

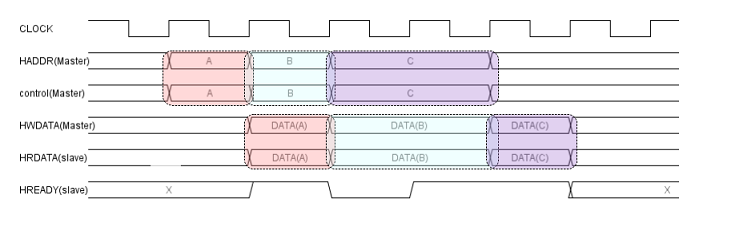

これで基本的な応答はできるようになりますが、以前説明したようにスレーブが即座にデータを返せない場合は、hreadyがアサートされます。その時は、マスターは出力データを保持せねばなりません。

これで、対応できました。