データパスのRTL

これまでに設計したデータパス部分をRTLで記述しました。

VHDLの記述の基本事項を知らないために、たったこれだけのものでかなりの時間を費してしまいました。

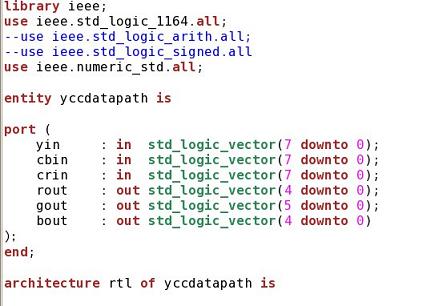

まずはライブラリの指定から。

最初の ieee.std_logic_1164.all は当然のように指定しましたが、演算に関して指定するライブラリがいろいろある模様。ライブラリの中身を見ていろいろお勉強しました。

符号つきの演算をしたいのですが、どうもどれを使うべきかはっきりしません。

最終的には、

http://dz.ee.ethz.ch/support/ic/hdl/vhdlsources.en.html

に以下の記述を発見。

std_logic_arithは標準化される以前にsynopsysによって開発されたもの。今後の開発にはieee.numeric_std.all を使用するべき。

よって、今後はこちらを使用します。

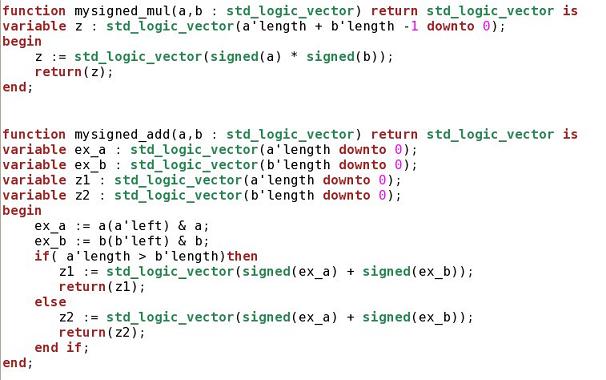

符号つきの乗算と符号つきの加算は明示的に function にしました。そのまま、*や+を使ってよいみたいですが、慣れていない私にはわかりずらいので別関数としました。

かつて、仕事でデータパスのハードマクロを設計していた時期がありました。論理を組んで、トランジスタをつなぎ合わせてSPICEでシミュレーションしてカスタムレイアウトしていました。

(アルゴリズム、論理の組み方、トランジスタのサイズ等をいろいろ検討してゴリゴリに高性能化を進めます。)

その時のイメージがあるので、どうもまだネットリストっぽく記述する方がしっくりきます。ここら辺が、VHDLに慣れてくれば短い行数の方がしっくりくるように変わってくるのではないかと予想しています。

ライブラリの中身を読んだところ、SIGNED型というのは std_logic_vector のSUBTYPEと呼ばれるもののようです。そして、signed(), std_logic_vector() のように型をキャストして変換できるみたいです。 ieee.numeric_std の中を読むと+や*は与える左右の変数の型によってそれぞれ定義されオーバーロードされている模様。よってSIGNEDにキャストして+*を使えばそれだけで演算できます。

Nビットの加算の出力が何故かNビットなので、1ビットづつ符号拡張してから+するようにしました。

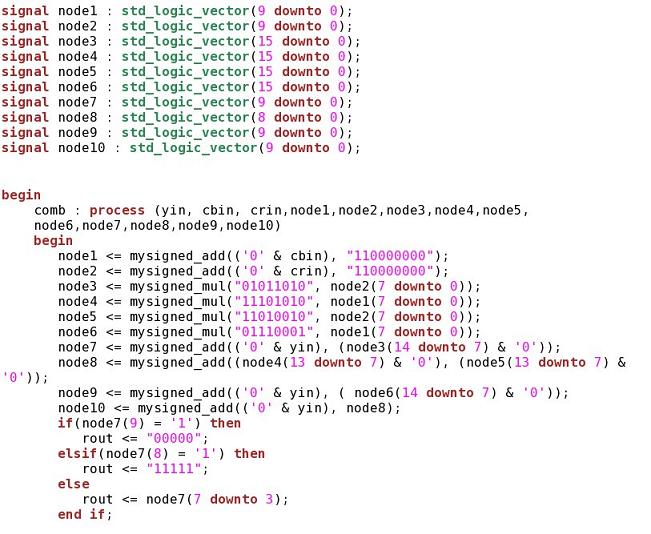

NODE…と中間変数を作り、ハードウェアを接続するように記述しました。

最初Process文の sensitivity リストに中間ノードを入れていなかったために、変な動作をしていました。これに気がつくのに、かなり時間を使ってしまいました。

どうやら、このような接続はprocess文を使わない方が普通のようですが、LEONでは、組み合わせ回路はひとつのprocessで記述することが多いので、それにならいました。

シミュレーションで正常動作が確認された後に procedure での記述に変更しようと思っています。

性能改善できる余地はいろいろあると思いますが、とりあえずはこれで進めて性能的に問題があれば、書き換えていきます。