LEONシステム FPGAマッピングとGRMON通信 GR-XC3S-1500(Xilinx)編

次はFPGAマッピングです。

これまでの作業と同じく、LEON/grlib-gpl-1.0.22-b4095/designs/leon3-gr-xc3s-1500 のディレクトリで作業を行います。まず、ISEへのパスが通っているか確認します。パスが通っていない場合は、

source /opt/Xilinx/11.1/settings32.sh

によってパスを通しておきます。

make ise-launch

と打ち込むと、ISEのプロジェクトファイルが作成され、自動的にISEのウィンドウが立ち上がります。

後は通常のISEのマッピングと同じく、generate programing fileをRUNさせるだけで、FPGAへ論理合成、配置配線を行って bit ファイルを作成してくれます。オプションを変更したい場合はRUNさせる前に行います。今回はオプションを変更する必要はありません。

ISEをバッチモードで動作させてウィンドウを立ち上げずにbitファイルまで作ってしまうコマンドも用意されています。慣れてきたらこちらに変更することも可能です。

たったこれだけでFPGAマッピングが終了しました。

IPの追加等を行ったときは、同じディレクトリにある ucf ファイルのピン配置を変更する必要があります。

公式サポートボード以外の場合は、似たボードの設定をコピーしてきて、ucfファイルを変更したりターゲットデバイスを変更したりする必要があります。

ここまで行ってbitファイルができたら、実際にマッピングします。

ボードに電源ケーブル、FPGAコンフィグケーブル、イーサネットケーブル、RS232Cケーブルを接続します。

(ディスプレイはこのタイミングでは必要ありません。)

私の場合は、digilent社のUSB-JTAGケーブルを用いていますので、SAMBA経由でウィンドウズにbitファイルを送り、digilent社のソフトAdeptを立ち上げてFPGAのコンフィグレーションを行いました。

Xilinxの純正ケーブルの場合はISEに付属しているIMPACTというソフトでFPGAのコンフィグレーションを行います。

また、RS232Cケーブルは私のPCにはRS232C端子が無いのでUSB-RS232C変換ケーブル(ATEN製)を使用しました。

ボード上の Done のLEDが点滅したらFPGAコンフィグレーション完了です。

ハードウェアが完成したので、ソフトウェアのコンパイルに進んでも良いのですが、ここでハードウェアがきちんと動作するか確認しておきます。

GR-XC3S1500は、gaisler research社からlinuxのコンパイル済みサンプルイメージをダウンロードすることができます。

LinuxのダウンロードページのSample Linux 2.6 images for LEON3の項から、GR-XC3S-1500用のコンパイル済みイメージ image.dsu をダウンロードしてきます。

このサンプルイメージはUARTにコンソール出力を行います。RS232Cをつないだホストコンピュータのwindows上にコンソール出力を表示するためのソフトteratermをインストールして準備しておきます。

teratermを立ち上げ、接続先をシリアル(私の環境では、COM3)に設定します。

teratermの"設定"プルダウンからシリアルポート設定を選択します。

ボー・レート 38400

データ 8bit

パリティ none

ストップ 1bit

フロー制御 none

に設定します。これでコンソール出力を表示する準備が整いました。

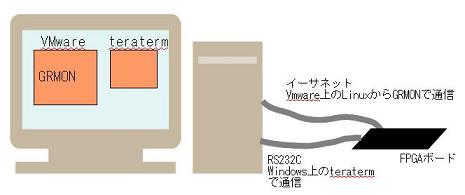

以下のような接続イメージです。

次にGRMONを立ち上げて、コンフィグレーションの時に出てきたDebug Support Unitと通信を行います。

grmon/grmon-eval/linux/grmon-eval -nb -nswb -eth -ip 192.168.24.10

と打ち込みgrmonを起動します。-ethに続けて打ち込むIPアドレスはコンフィグレーションの時に出てきたEDCLのIPアドレスです。無事にFPGAボードのEDCLと通信ができると以下のようなメッセージが出力されて入力受付状態になります。

GRMON LEON debug monitor v1.1.41 evaluation version

Copyright (C) 2004-2008 Aeroflex Gaisler - all rights reserved.

For latest updates, go to http://www.gaisler.com/

Comments or bug-reports to support@gaisler.com

This evaluation version will expire on 28/1/2011

ethernet startup.

GRLIB build version: 4095

initialising ...............

detected frequency: 40 MHz

Component Vendor

LEON3 SPARC V8 Processor Gaisler Research

AHB Debug UART Gaisler Research

AHB Debug JTAG TAP Gaisler Research

SVGA Controller Gaisler Research

GR Ethernet MAC Gaisler Research

ATA Controller Gaisler Research

LEON2 Memory Controller European Space Agency

AHB/APB Bridge Gaisler Research

LEON3 Debug Support Unit Gaisler Research

Generic APB UART Gaisler Research

Multi-processor Interrupt Ctrl Gaisler Research

Modular Timer Unit Gaisler Research

PS/2 interface Gaisler Research

PS/2 interface Gaisler Research

General purpose I/O port Gaisler Research

Use command 'info sys' to print a detailed report of attached cores

grlib>

ここでinfo sysと入力すると、現在のFPGAにマッピングされているLEONシステムの構成がレポートされます。

grlib> info sys

00.01:003 Gaisler Research LEON3 SPARC V8 Processor (ver 0x0)

ahb master 0

01.01:007 Gaisler Research AHB Debug UART (ver 0x0)

ahb master 1

apb: 80000700 - 80000800

baud rate 115200, ahb frequency 40.00

02.01:01c Gaisler Research AHB Debug JTAG TAP (ver 0x0)

ahb master 2

03.01:063 Gaisler Research SVGA Controller (ver 0x0)

ahb master 3

apb: 80000600 - 80000700

clk0: 25.00 MHz clk1: 40.00 MHz clk2: 50.00 MHz clk3: 65.00 MHz

04.01:01d Gaisler Research GR Ethernet MAC (ver 0x0)

ahb master 4, irq 13

apb: 80000d00 - 80000e00

edcl ip 192.168.24.10, buffer 2 kbyte

05.01:024 Gaisler Research ATA Controller (ver 0x0)

ahb master 5, irq 10

ahb: fffa0000 - fffa0100

Device 0: (None)

Device 1: (None)

00.04:00f European Space Agency LEON2 Memory Controller (ver 0x1)

ahb: 00000000 - 20000000

ahb: 20000000 - 40000000

ahb: 40000000 - 80000000

apb: 80000000 - 80000100

8-bit prom @ 0x00000000

32-bit sdram: 1 * 64 Mbyte @ 0x40000000, col 9, cas 2, ref 7.8 us

01.01:006 Gaisler Research AHB/APB Bridge (ver 0x0)

ahb: 80000000 - 80100000

02.01:004 Gaisler Research LEON3 Debug Support Unit (ver 0x1)

ahb: 90000000 - a0000000

AHB trace 128 lines, 32-bit bus, stack pointer 0x43fffff0

CPU#0 win 8, hwbp 4, itrace 128, V8 mul/div, srmmu, lddel 1

icache 2 * 4 kbyte, 32 byte/line lru

dcache 1 * 4 kbyte, 16 byte/line

01.01:00c Gaisler Research Generic APB UART (ver 0x1)

irq 2

apb: 80000100 - 80000200

baud rate 38461

02.01:00d Gaisler Research Multi-processor Interrupt Ctrl (ver 0x3)

apb: 80000200 - 80000300

03.01:011 Gaisler Research Modular Timer Unit (ver 0x0)

irq 8

apb: 80000300 - 80000400

8-bit scaler, 2 * 32-bit timers, divisor 40

04.01:060 Gaisler Research PS/2 interface (ver 0x2)

irq 4

apb: 80000400 - 80000500

05.01:060 Gaisler Research PS/2 interface (ver 0x2)

irq 5

apb: 80000500 - 80000600

08.01:01a Gaisler Research General purpose I/O port (ver 0x0)

apb: 80000800 - 80000900

grlib>

接続された各種IPのAMBAアドレスが表示されました。

それでは、先ほどダウンロードしてきたlinuxイメージimage.dsuをFPGAにロードして実行します。

load image.dsu

run

と入力するとlinuxのブートがはじまり、teratermに続々とlinux boot messageが流れていきます。

無事にブートできteraterm上てlinuxのコマンド受付状態になればブート成功です。

これで、FPGAにマッピングしたハードウェアが正しく動作していることが確認できました。

今回はコンパイル済みのlinux imageを動作させただけですので、次のエントリから自分でlinuxをコンパイルしてブートイメージを作る方法に入ります。