64画素メモリ

複数のjpeg画像ファイルでハフマンデコードが問題なく行われていることが確認できました。

これまでの方針で一応ハフマンデコードできると考えられます(バグはまだ入っている可能性大)。

しかし、FPGAにインプリしてまともに動くかどうかはまだ分かりません。

クリティカルパスがどれぐらいかも分かっていませんので調べる必要があります。

そこで、ハフマンデコード部分と、IDCT以降をつなぐ64画素メモリとコントローラ部分をコーディングしてつないだ上でISEでマッピングして調べてみようと思います(現在のFPGAには入らないと思いますが、大体のあたりをつけることができます)。

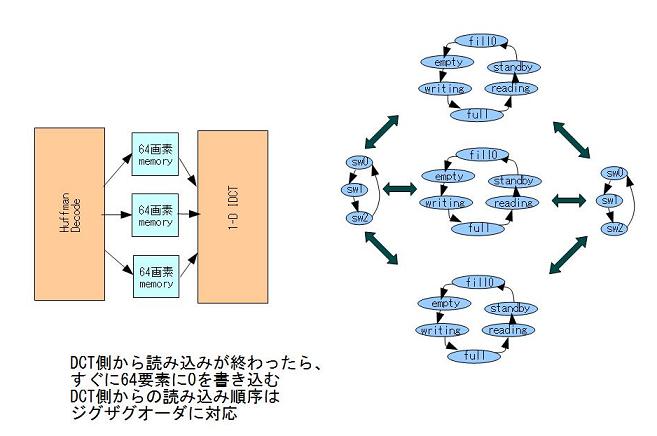

64画素メモリは以下の図のように以前設計したものをモディファイしたものにします。

ランレングス部分は書き込まずに値があるところだけを書き込むように設計したため、最初に64要素に0を書き込む必要があります。書き込む要素が少ないブロックでは、こちらの時間の方が重くなることもありえます。よって図のようにメモリを3つにしました。

現在のシステム構成では、ソフトウェアでハフマンデコード部分にデータを送るので、かなり飛び飛びにデータが送られることになり、メモリ二つでも性能は変わらないと思いますが、データが大量に送られてきているとき性能がでるように設計する方針なのでメモリ3つにしています。

これは、以前のものを軽くモディファイすればできるので、コーディングしてISEに掛けてみようと思います。