ハフマンデコードモジュール 4 (キャッシュ)

シリアルに順にチェックしていくルーチンも、それほどクロック数を必要としないみたいなので、IJGと同じくキャッシュは8bitにしようと思います。

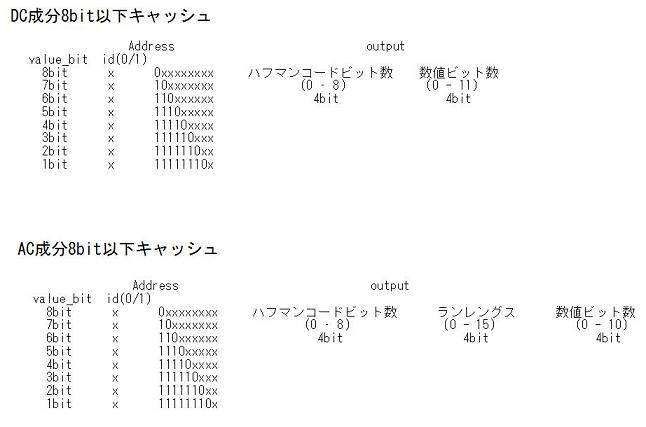

IJGでは、8bitでキャッシュにヒットしなかった場合とバッファに8bit未満のデータしかない場合にシリアルチェックの関数をコールしています。しかし、ソフトウェアでは大きなバッファを持っていますので、そこにあるデータが8bit未満ということは、そうそう発生しません。一方で現在設計中のハフマンデコードモジュールは32bitのフェッチレジスタにデータが格納されているため、8bit以下の状態が起きる確率はIJGソフトウェアよりもだいぶ大きいと考えられます。よって、8bit以下の場合のキャッシュを構成することにしました。

キャッシュブロックに現在のvalue_bitの値と共にコードを入力します。

value_bitが7以下の場合はアドレスに判別できる符号が付きます。図のアドレスの中でxの部分がコードが入力される部分です。

また、AC,DCそれぞれ二つづつ必要になります。DC用にはランレングスの情報は必要ないため、AC,DCでそれぞれメモリを別にします。それぞれの二つのデータはアドレスの先頭ビットにidを入力することで判別します。

このようにデータを持つことで、8bit以下のコードは必ずヒットします(フェッチレジスタが8bit無い場合には、リクエストしたbit以下のコードのみ必ずヒットします)。キャッシュアクセスでハフマンコードビット数で0が返ってきた時は、コードが要求したビット数以上のものであることになります。