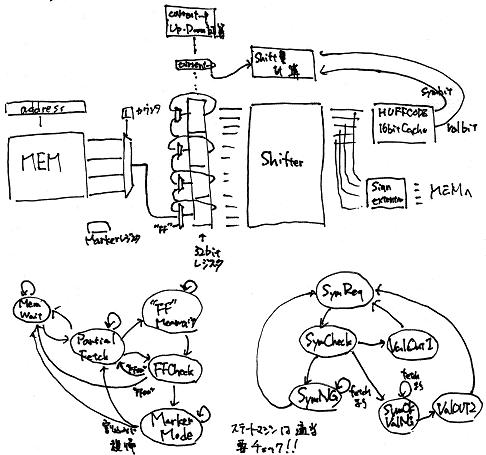

ハフマンデコードモジュール 構成案修正

とりあえず、フェッチレジスタ32bitでフェッチ単位が8bitのものの構成を考えました。

(ステートマシンは適当です。これから詳細調べます)

フェッチを8bit単位にしたので、フェッチするさいに"FF"を検出します。

"FF"を検出した場合、次に"00"であれば、FFを書き込んで通常のフェッチ状態に戻ります。

次が"00"で無い場合は、その値をMarkerレジスタに書き込んで、Marker Modeになります。 Marker Modeでは、32bitフェッチレジスタの有効ビット数が減ってもメモリからのフェッチは行いません。

Marker Mode かつ、フェッチレジスタ有効ビットが0になった場合は割り込みを発生します。マーカー処理はソフトウェアで対応。その後ソフトウェアからの書き込みによって通常状態に復帰。

マーカーの前にパッディングビットが入る可能性がありますので、割り込み発生条件は有効ビット数0だけではありません。けど、ちょっとここら辺のJPEG仕様の理解があいまいなので調べないといけません。。。。。

データがある限り、8bitのフェッチを連続で行えるように考えたつもりなので、フェッチレジスタを32bitにしてもそれほど性能劣化しないつもりです。しかし、詳細を考えて本当にきちんと動くかチェック必要です。

フェッチレジスタを40bitにした方が性能が良ければ簡単に変更できます。

詳細検討の前に32bitのシフタがどれぐらいのサイズになるかRTL書いて配置配線して調べたいと思います。