IDCT モジュール RTL

頭の中にこれまでの設計があるうちにコーディングしてしまいたいため、msys上のパスの問題は、makeにより出力されるスクリプトファイルを強引にエディタで書き換えてmodelsimを立ち上げました。

(とりあえず応急処置。今のうちにコーディングしておきたいので。)

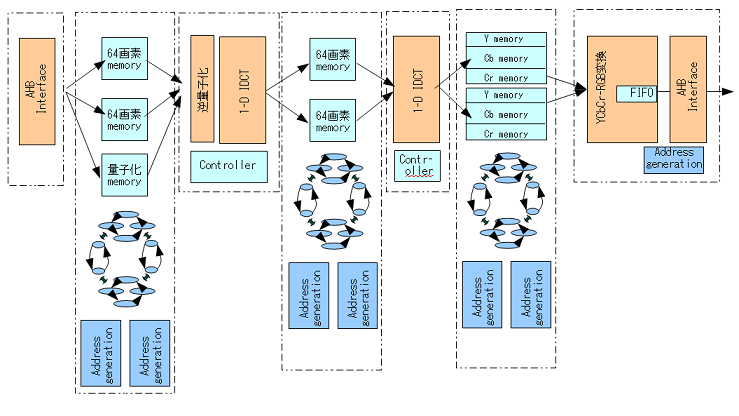

この中で、DCTメモリ+コントローラ2個と、IDCT2個をコーディングしました。

すべて、ready,strobe で通信するように設計しています。

IDCTの方はデータパスはすでに設計済みですので、ready, strobeによる通信部分をほんの少し追加するだけで完成です。

IDCT二つ接続した状態で、テストベクタを入力するテストベンチを流しました。やはり、IJGの出力に対して誤差があるのですが、自分が書いたハードウェア確認ソフトの出力ほどではありません。殆どの誤差が±1 に収まっています。これは、ハードウェア確認ソフトの方がバグ有りで、RTLの方はバグはないけど、丸めでどこかに少し誤差が乗っている可能性が高いなーと思いました。

DCTメモリ+コントローラ部分は、以前のYCbCrメモリ+コントローラ部分を変更することによって設計できます。どちらもここで、行列転置の機能を持ちます。Address generationによりその機能が実現されます。非常に簡単です。

上図のように新しく設計した部分を挿入して、AMBAマスタエミュレータを接続して、テストベクタファイルを入力して検証します。まだ誤差があるので検証が難しいのですが(YCbCr-RGB変換をすると誤差がどれぐらいか判別が難しくなる)、それなりの値が出力されているようです。

そこで、FPGAに入るかどうかが大きな懸念事項なため、ISE10.1でマッピングしました。

出力結果は、、、、 occupied Slice 99%!!! タイミングエラー無し

何とかなったかと思ってFPGAにコンフィグレーションしたのですが、うんともすんとも言ってくれません。

良く P&R レポートを見てみると、、、、、、

Phase 1.1

ERROR:Place:665 - The design has 31 block-RAM components of which 14 block-RAM components require the adjacent multiplier site to remain empty. This is because certain input pins of adjacent block-RAM and multiplier sites share routing ressources. In addition, the design has 21 multiplier components. Therefore, the design would require a total of 35 multiplier sites on the device. The current device has only 32 multiplier sites.

と乗算器とメモリの合わせた数の制限を超えているというメッセージが、、、、、

Sliceは、まだ減らせるモジュールがあるので何とかなると考えていたのですが、乗算器とメモリが両方100%使えないという事実を始めて知ってしまいました。

うーん、キャッシュを減らすぐらいしか思いつかないなー。あとはモジュール削ってSlice減らして固定ビット乗算器を組み合わせ回路で記述するぐらいか。

しかし、この後ハフマンデコーダが入ることを考えるともっと良いボードを購入したいなとも考え始めました。

うーん。