YCbCrメモリ+コントローラ 修正

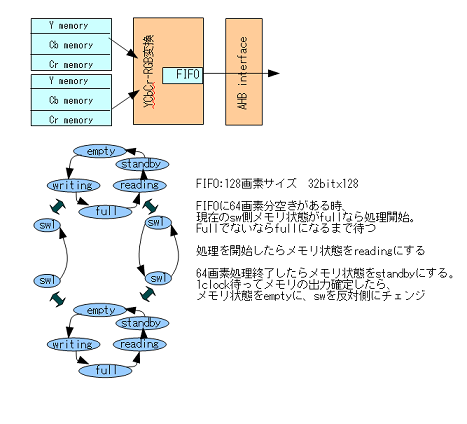

readingからemptyに移る間に一つ何もしないステートを追加しました。

この間にメモリの出力を確定させます。メモリ出力はアドレスやenableを入れた次のクロックで確定しますので、確定してからスイッチを切り替えます。

メモリのアドレスカウンターを1ビット増やして対応しても良いのですが、こちらの方が修正が少なくてすむためにこちらを選びました。

そして、このエントリのように、AMBAマスタエミュレータと接続して、検証します。

この時の入力テストベクタは、IJGのDCT関数(jidctint.c)のDCT計算終了後の部分をファイル出力してつくります。

また、期待値ベクタは、以前と同様にjdcolor.c中のハードウェアエミュレーション記述した部分から出力しますが、今回は少し変更が必要となります。

というのは、今回のハードウェアはYCbCr-RGB変換のみだけではなく、upsamplingの機能も有しています。IJGのupsampleは4:2:2, 4:1:1 それぞれの場合に、h2v2_fancy_upsample(), h2v1_fancy_upsample()という関数で処理をしていますが、単なるアップサンプルだけではなく、補正を掛けている模様です。

補正を掛けない関数として、h2v2_upsample(), h2v1_upsample()という関数がありますので、こちらをコールする必要があります。

私は、関数名セットする部分を変更したくなかったので、h2v2_fancy_upsample()の中身を消して、h2v2_upsample()の中身をそのまま、そこにコピーするという腕力的な手法で単純なアップサンプルを行いました。

このようにして得られた期待値と比較しながら、AMBAマスタエミュレータで出力結果を格納しているアドレスを読み込むと期待値と一致しました。

日曜工作ですので、検証はそれほどきちんと行わずに、絵が出れば良いというような感覚で進めてきましたが、そろそろ規模も大きくなってきていますし、モジュール同士が自律的に通信するような設計になっていますので、様々な通信の状況を作り出すような検証もした方が良いような気もします、、、、

ちょっと悩みどころなのですが、今回はこのまま行けるところまで行きます。

(最終的にはやらないといけないだろうなー、、、、)

次に、このエントリのように、入力ベクタを配列に変更してシステム検証ソフトを作り、GHDLを用いてシステムとして動作させてみます。

無事、GPIOにモジュール計算後の値が出力されていることがgtkwaveで確認できました。

要素技術をすでに習得していますので、少しづつ変更するだけで対応できます。

ここまでくればFPGAのインプリです。ISEを動かしてビットファイルを作りました。以前と異なるwarningがいろいろ出ているなーと思っていたら、FPGAにマッピングしても全く通信できません、、、、、、

よく分からないので、modelsimでシミュレーションをぶん回そうとすると、、、、、

また、以前起きたように、ファイルがあるのに、File not foundのエラーが大量にでます。

msysに変更してもだめなようです。

makeの中で行われている、windows上のパスと、msysやcygwinm上のパスの変換が、ISEを立ち上げるとおかしくなってしまうのかもしれません、、、、

しかし、対策が全く分かりません。

いずれにしろ、少し行き詰ってしまいました。

msysm上では、modelsimのみの実行にして、ISEはVMware上のLinuxで行うというのが一番簡単な回避策のような気もします(grlibはgnumakeに依存していますので、linux上が一番安定しています)。そうすると、かなり重たい処理であるISEmが仮想OSの上で実行されてしまうのでかなり損をしてしまうのですが、、、、

そうするにしても一度cygwinまたは、msysをインストールしなおすしか、modelsimを動作させる方法が今のところ思いつきません。

今頃ここに来て、開発環境の問題が大きくのしかかってきました。

困った。。。