フロー制御

YCbCr-RGB変換回路を修正するためには、全体のフローをきっちり理解する必要があります。

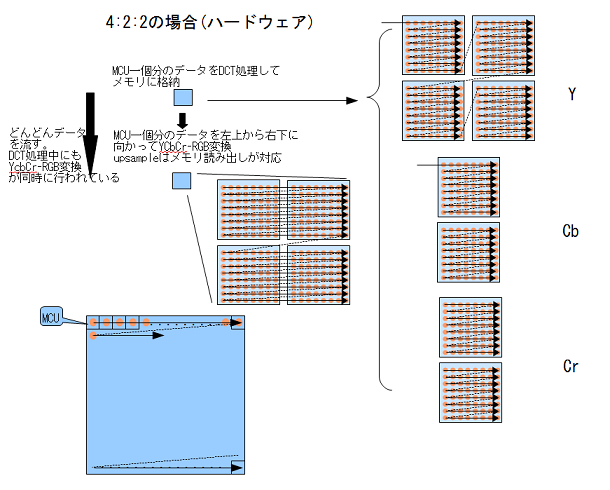

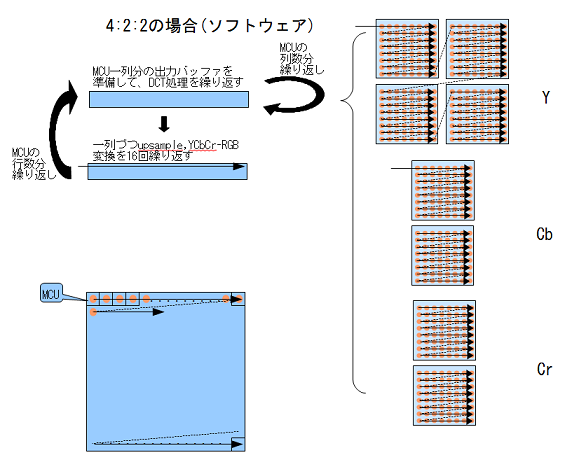

以下は、IJGのdjpegにおけるJPEG処理フローです。4:2:2の場合を説明しています。

ソフトウェア中では、MCU一列分のDCTが行われて、その後ピクセル画面一列分を順にYCbCr-RGB変換を行っています。そして、その処理をMCUの列数分繰り返しています。

ハードウェアにする際に、MCU一列分のメモリを持つことは、非常に大きなコストとなります。内部にSRAMとして持てる容量には制限がありますし、DRAMに一々書き出してはレイテンシも大きいですし、バスの大域も圧迫します。ハードウェア処理の場合は、MCUサイズ分のメモリを持ちます(ダブルバッファにしますので、実際はMCU2個分になります)。

MCU一個分づつ、DCT,upsample,YCbCr-RGB変換が次々と行われます。

ハードウェアの場合は、YCbCr-RGB変換中にも次のMCU分のDCT処理が実行されていることが大きなポイントです。

このようなフローにした場合には、YCbCr-RGB変換回路のアドレス生成は、図のように横16ピクセル分の出力を8回繰り返すようになります(一回で2pixel分32bit出力するため)。そして、出力し終えた時に次のMCUの先頭アドレスになります。

また、MCUが一番右端まで出力した時は、次のMCUは一つ下の一番左上のアドレスに変わります。

このようにアドレス生成部を変更する必要があります。

また、upsampleはメモリアクセスによって実現されます。ここにもアドレス生成が必要となります。

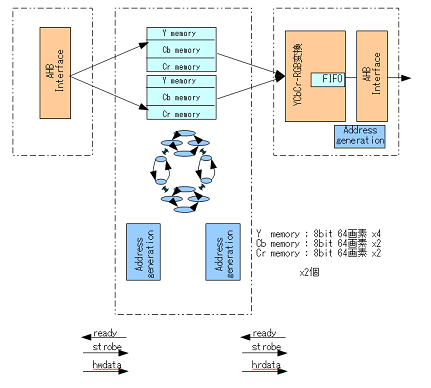

このような状況で、まず最初に以下のようなものを設計することにしました。

上記のように、AHB interface, YCbCrメモリ+コントローラ, YCbCr-RGB変換モジュールに分割して設計します。YCbCrメモリに対するアドレス生成とメモリ状態FSMを一つのモジュールとし、それぞれのモジュールのインターフェースは、ready,strobe,dataのみにします。

このように設計することで、AHB interfaceとYCbCrメモリ+コントローラの間にDCTモジュールやメモリを挿入するだけで、DCT処理以降のハードウェアに変更することが可能になります。

また、このように設計したものをLeon Systemに接続して、ソフトウェアDCT処理終了したタイミングでデバイスドライバでハードウェアに転送して画面を確認することで、アドレス生成がきちんと行われているかの確認もできるため、丁度良い設計の中間マイルストーンになります。