IDCTデータパス RTL

IDCTのデータパス部分のコーディングを行いました。

一部修正しています。

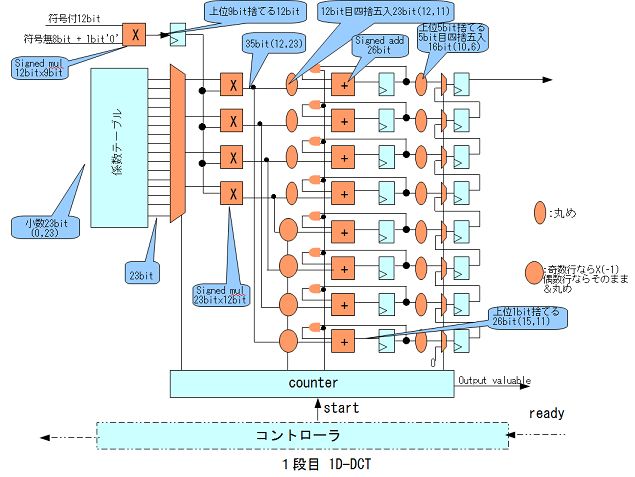

一段目:

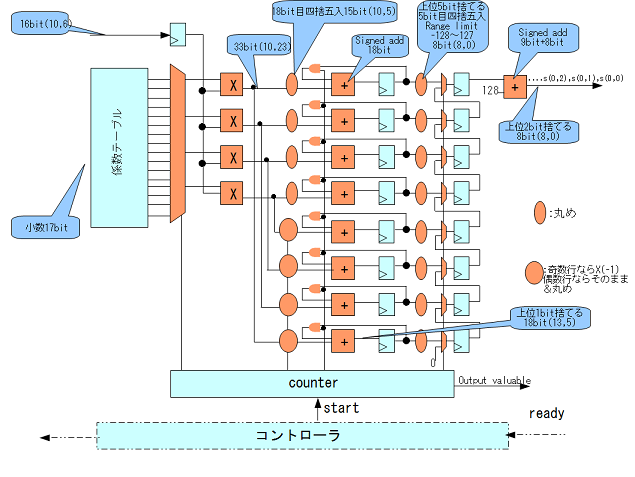

二段目:

データパスですが、コントロールFSMが必要となります。図中のcounterの部分が外部からのstart信号により動き始め、その値によって、各セレクタ等が動作を決めていきます。また、出力が有効であるという信号もcounterから出力しています。この信号は後段メモリに書き込む際に使用します。

面積縮小のため、係数テーブルから受けていたFFをなくしています。入力と1cycleずらして出力するようにテーブルのセレクタを設計します。ちなみに設計後に簡単にISEを実行してみたところ、カウンターの出力から係数テーブルセレクタや乗算器や加算器を通ってアキュムレータに通じるパスがクリティカルパスとなり、約21nsでした。これまでのクリティカルパスは約20nsだったので、今のところチップ全体のクリティカルパスとなってしまいます。これまで、40MHzで動かしていましたが、ボードのクロックオシレータの出力は50MHzですので、うまく行けば50MHz動作可能と思っていたのでちょっと残念です。しかし、まだ合成やルータのパラメータはいじっていませんので、今後50MHzが可能になる可能性もあります。今後、バスが厳しくなった場合、ビデオ信号クロックは一定値なので、システムクロックが上がるとデータパス処理能力向上よりも大きく向上する可能性があります。

もし、最終的に50MHzが不可能で、かつ面積があまった場合は、ここに再びFFを入れなおすつもりです。

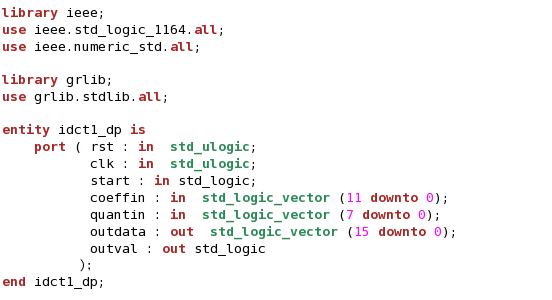

入出力ピンは以下のようになります。FSMがありますので、clk,rst信号が必要となります。

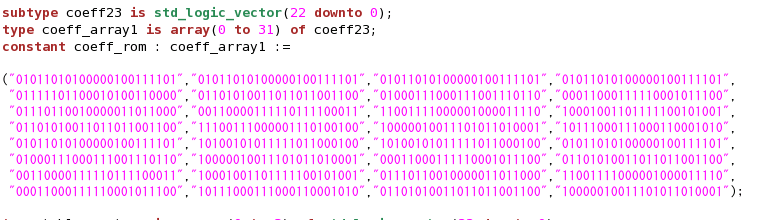

係数テーブルは以下のように単純な2次元配列を用いました。

これをカウンターの出力値によって出力を選びます。

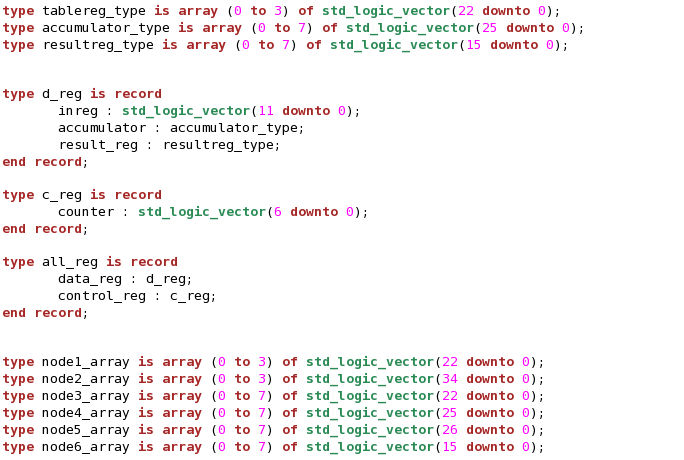

レジスタや、データパス中の中間変数ようの定義も2次元配列でおこないます。

このように2次元配列で記述しておけば、データパス部分のコーディングにforループを使えます。

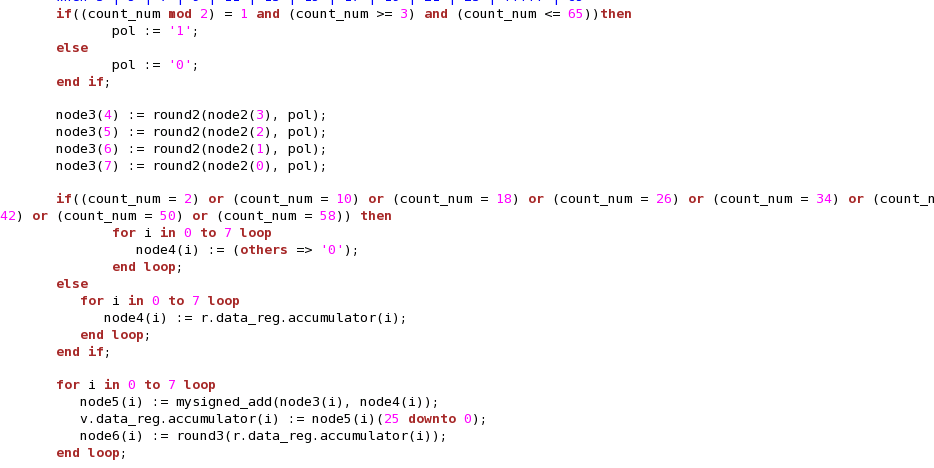

データパス接続部分の一部を下記に示します。

(多分、ISEは理解してくれるんじゃないかなー??)

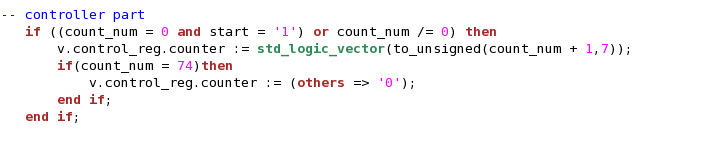

あと、カウンター部分も。

カウンターが0の時にstartがアサートされるとカウントアップが始まります。

start部分がいつアサートされるかは、前回の全体制御フローで決まります。その部分は含めていません。

こうやってデータパス部分のみRTLコーディングした後に、以前のYCrCb-RGB変換モジュールで行ったように、C言語でコーディングして作ったテストパターンを入力して一致するかチェックします。

すでに必要な要素技術を手に入れていますので、簡単に進んでいきます。

が、、、、、、、、

出力値が一致しない、150回に一度ぐらいの割合で出力が1違うものが出ています。これは多分丸めの問題だと思いますが、、、、、

以前書いたように、私がコーディングしたC言語記述ハードウェアエミュレート部分の方に誤差があるのかもしれず、どちらが神様データか分かりません。誤差については動いてからもう一度徹底的に考えるつもりですので、とりあえずこのまますすめます。

これらのRTLを少し書き直すだけで2段目のDCT部分のRTLが完成します。こちらも同じようにごくたまに誤差が載っています。ここもとりあえずこのまま進めます。

さて、これで全体をつないでといきたいのですが、実はYCbCr-RGB変換モジュールを大幅に改造しなければなりません。というのは、IJGのソフトウェアでは、MCU単位の処理を横一列分バッファにためてから、サンプリング、色変換に一行づつデータを送るという処理順序となっています。現在のYCbCr-RGB変換モジュールも横一列の順でデータを受け取ります。これをMCU単位の処理データにあわせてFrameBufferに書き出すように、アドレスジェネレーション部分の変更が必要になります。

次は、この変更を行います。