YCbCr-RGB変換モジュールRTL システム検証 1

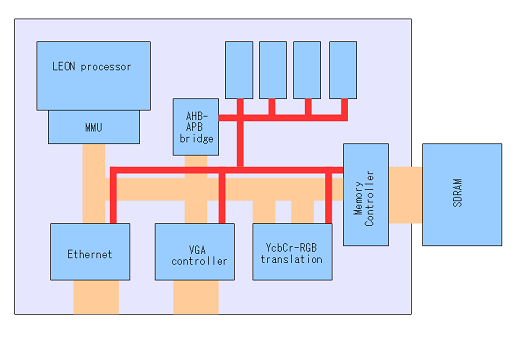

GHDLでYCbCr-RGB変換モジュールを接続したシステム(leon3mp.vhd)全体のシミュレーションが動き始めました。このシステムの全体像は次の図のようなものです。

この全体がHDLシミュレーションで動作しています。SDRAMもメモリベンダから提供されているVHDLモデルを使用しています。その際に、sdram.srecというファイルをSDRAMの中身としてインクルードしています。

このファイルは、$GRLIB_HOME/design/work/sdram.srec を見ると分かりますが、コンパイルされたテストプログラムのバイナリです。同じディレクトリにsystest.cというファイルがありますが、これは、design毎に与えているテストプログラムが異なるためにここに置いて中身をチェックできるようにしています。

実体は、$GRLIB_HOME/software/leon3 のディレクトリを見ると分かります。レジスタファイルのテスト、乗算器のテスト、イーサネットのテスト、などのソースコードがあります。アセンブラファイルも結構あります。ここでdesignにあった適当なものを選んで、makeすることにより、sdram.srecができます。

SDRAMにこの内容が書かれている前提でシミュレーションが動いていますので、例えばイーサネットのテストならば、Leon processorがSDRAMにリード、ライトしながら、イーサネットコアを動かして接続や動作を確認している訳です。

という訳で現在動いているGHDLのトップシミュレーションは、YCbCr-RGB変換モジュールの検証にはまったくなっていません。ここに適当なプログラムを書いてモジュールにアクセスしてチェックするプログラムをコンパイルし、sdram.srecとして、アサインして動作させて、初めてモジュールのシステム検証ができたことになります。

このコンパイルには、Bare-Cコンパイラという、gaisler reseachから提供されているC言語コンパイラを用いています。これは、Linux等のOSが無い状態のLeon processorで動くバイナリを生成するためのコンパイラです。仮想アドレスがありませんので、おそらく物理アドレスにポインタアクセスすることにより直接データをモジュールに書き込めると予想しています。これから調査開始です。

しかし、アセンブラ使わないといけなったら、また少しハードルがあるなー。。。

おまけ:

modelsimでは、全体のシステムシミュレーションが行数制限で動かないと書いていましたが、昨日の夜寝る直前に開始したシミュレーションが朝起きると無事終了していました。行数制限を越えると極端に実行速度が落ちるだけで、動くことは動きました。昨日の夜、シミュレーションが少しづつ進んでいるようでしたので試してみました。これで、最悪、modelsimでも中の動作を追うことができるので、かなり安心しました。

しかし、最初の頃使用していた性能の低いPCでは、シミュレーションが進むそぶりさえなかったのに、数時間で終わってしまうなんて、さすが、QuadCoreだなーと思いました。

やはり、技術の進化にはついて行かないといけないようです。