YCbCr-RGB変換モジュールRTL AMBA slave 1(仮)

まず、AMBAバスの構造から。

AMBAの仕様書より。

AMBAは完全にフリーで公開されています。

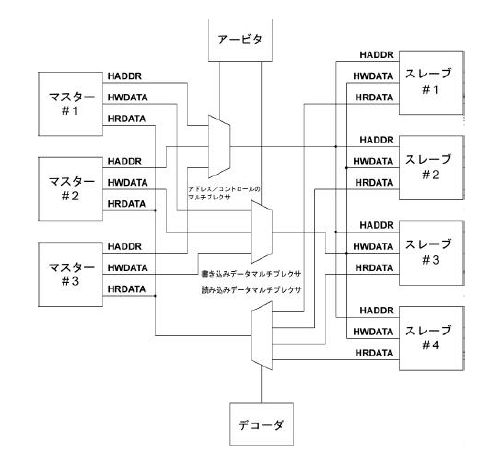

まず最初にマスターがバスの使用をリクエストします。アービタが何かしらのアルゴリズムで許可するマスターを選択し、GRANT信号をマスターに与えることによって通信が開始されます。

この図では、マスターから出力アドレスを示すHADDR、書き込みデータを示すHWDATAが出力されています。その他に、転送タイプ等を示す多数のコントロール信号等が出力されます。それらの信号は単純なマルチプレクサによってバスを獲得したマスターからの信号のみが選ばれて全スレーブに供給されます。

リード命令の時には、逆にスレーブ側からHRDATAが出力されます。このデータも単純なマルチプレクサによって現在呼び出されたスレーブからの出力のみが選択されるようになっています。

その他、非常に重要な信号として、各スレーブから出力されるHREADY信号があります。これは、スレーブが書き込み読み出しが間に合わない時にアサートしてマスターに現在の転送状態を維持してもらうための信号です。この信号はすべてのスレーブから出力され、選択された後にすべてのマスターとスレーブに入力されます。

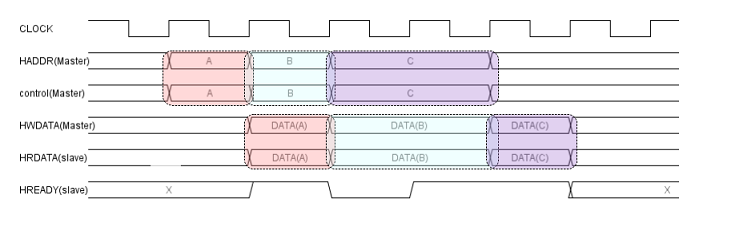

これがもっとも単純な転送のタイミングダイアグラムです(HRDATAとHREADYはスレーブから出力されることに注意)。

マスターがバスを獲得した後の部分を図に示してあります。

?で、マスターはあるアドレスに対して操作を行なおうとしてアドレス番地を出力しています(control信号の中に読み出しか書き込みか判断する信号があります)。

?で書き込みの場合はマスターがその書き込む値を出力します。読み出しの場合はスレーブがその値を出力します。

このようにまずアドレスフェーズがあって、次にデータフェーズがあるのがAMBAの基本的な構造です。

次にスレーブが処理が間に合わない時に転送を延長した場合の状態が示されています。

先ほどと同様に?でマスターがアドレスBに対して書き込み、又は読み出しの信号を出力しています。

?で書き込みの場合はマスターが書き込みデータを出力していますが、スレーブが次のクロックで対応できないということをHREADYをLOWにしてマスターに示しています。

この書き込みデータは受け取ることができません。また読み出しの場合は読み出しデータをこのタイミングで出力することができません。

HREADYがLOWであることを受け取ったマスターは?で先ほどのアドレスフェーズの信号を維持し続けます。この延長はHREADYがHIGHになるまで続きます。

後記: この?は間違い。延長はありません。最初のアドレスフェーズと同じときにHREADYがLOWの時(一つ前のデータ転送延長の時)アドレス信号延長されます。後で図を直します.

?でスレーブの準備がととのったため、HREADYにHIGHを出力し、読み出しの場合はデータを出力します。書き込みの場合はこのタイミングでバス上に出力されているデータを取り込んで書き込みます。

つぎの図は転送が3つ続けて行われている場合のタイミングチャートです。

転送が連続する場合は、図のようにアドレスフェーズとデータフェーズが重なり合って出力されます。

この方法をとらないとバスの利用効率が悪化するためです。

よって、あるタイミングで、アクセスするアドレスと一つ前のデータが同時に存在します。

以上がAMBAバスの基本構造です。

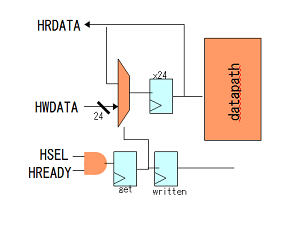

このようにアドレスフェーズとデータフェーズがあることから、AHBにSRAMをつなげることを考えると次のようなスレーブインターフェースが必要となることが分かります。

Writeの時は、一つ前のアドレス情報を保持しておき、データが到着すると同時にSRAMに書き込む。

Readの時は、アドレスが到着すると同時にメモリをリードし、次のクロックでデータを出力します。

また、WriteとReadが続けてきた場合は、メモリに同時に読み書きアクセスできませんので、一旦Hreadyをアサートしてマスターに転送延長を知らせる必要があります。

このように少しめんどくさくなるので、とりあえずレジスタで受けるものを設計しました。

このようにすると非常にシンプルになります。HSELとHREADYがアサートされた時のみ次のクロックでデータを取り込みます。それ以外はデータレジスタは値をキープ。

どのクロックで書き込まれたかが必要となるので、書き込まれたタイミング保持用のFFが一つ。

簡単に設計できます。

※しかし、設計した後にAMBAの仕様書を読みましたが、転送の終了の仕方の定義がはっきりしていない。。。 転送開始と転送終了で即座に次に移らずに状態を維持することが許されていると、この設計では、繰り返し書き込まれることになって誤動作します。

GrlibのRTLを勉強のために大量に読みましたが、このような受け方をしているものは皆無でした。もしかしたら、AMBA準拠とは言えないかもしれません。

ただし、実装するときに状態を保持し続けるマスタを設計することはおそらくないと感じるのでこのまま続けます。どっちみちDCTコアを設計すればメモリ受けになりますので、とりあえずソフトとつなげるところまでは見切り発車です。