データパスのテストベンチとFPGAへのインプリメントテスト

できあがったデータパス部分が正しいか論理検証を行います。

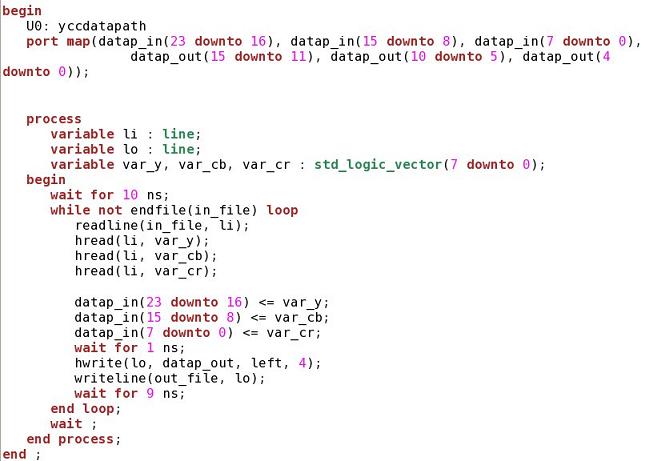

このような記述で、以前にIJGを変更してC言語で生成したYCC-RGB変換モジュールへの入力ベクトルをファイルから読み込み、出力される値をファイルに書き出します。

そして出力されたファイルを同様に以前生成した出力ベクトルファイルとDIFFをとることにより、このデータパス部分の正しさが確認できました。

そしてためしに、ISEを起動してこの部分を論理合成、配置配線を行ってみました。

すると、、、、、

*の部分を論理合成ツールが認識してFPGA内部の乗算器をマッピングしてしまいました。。。。

1や0固定値の伝搬はまず最初に行ってくれると思っていたので意外です。

ここで乗算器を使うのはもったいないような気がします(面積、スピードともに)。

乗算器の推定を避ける方法が何かあると思いますが、いまのところわかりません。

(固定値を伝播させて論理縮小した時の面積、スピードと比較したいのですが、、、、、、)

STAの結果は20nsでした。何の制約条件も与えずに20nsecですから、速度的には特に頑張って速くする必要はないかもしれません。(正確には、回りのモジュールも論理合成、配置配線しないと分かりません。)

スローなペースですが、少しづつRTL設計の感覚をつかんでいっている気がします。